In this article, we will explore the working of the SR Latch, its truth table, its implementation using NAND and NOR gates, and the differences between an SR Latch and an SR Flip-Flop. The SR Latch is one of the most fundamental building blocks in digital electronics. It is a type of bistable multivibrator, meaning it has two stable states that it can maintain indefinitely until an external signal forces it to change. The SR Latch is widely used in memory circuits, control circuits, and as a basic element in more complex sequential circuits like flip-flops.

1. What is an SR Latch?

An SR Latch (Set-Reset Latch) is a simple circuit that can store one bit of information. It has two inputs:

- S (Set): Used to set the output to logic ‘1’.

- R (Reset): Used to reset the output to logic ‘0’.

It also has two outputs:

The SR Latch maintains its state (either Q = 1 or Q = 0) until it receives a signal to change. The two inputs, S and R, are used to control the state of the latch.

2. Working of SR Latch

The SR Latch can be implemented using either NOR gates or NAND gates. The working principle remains the same, but the logic levels and truth tables differ slightly.

Basic Working Principle

- When the Set (S) input is activated, the output Q becomes ‘1’, and Q’ becomes ‘0’.

- When the Reset (R) input is activated, the output Q becomes ‘0’, and Q’ becomes ‘1’.

- When both inputs are ‘0’, the latch maintains its previous state (this is called the “hold” condition).

- When both inputs are ‘1’, it results in an invalid state (for NOR-based latches) or a “race condition” (for NAND-based latches), which is generally avoided.

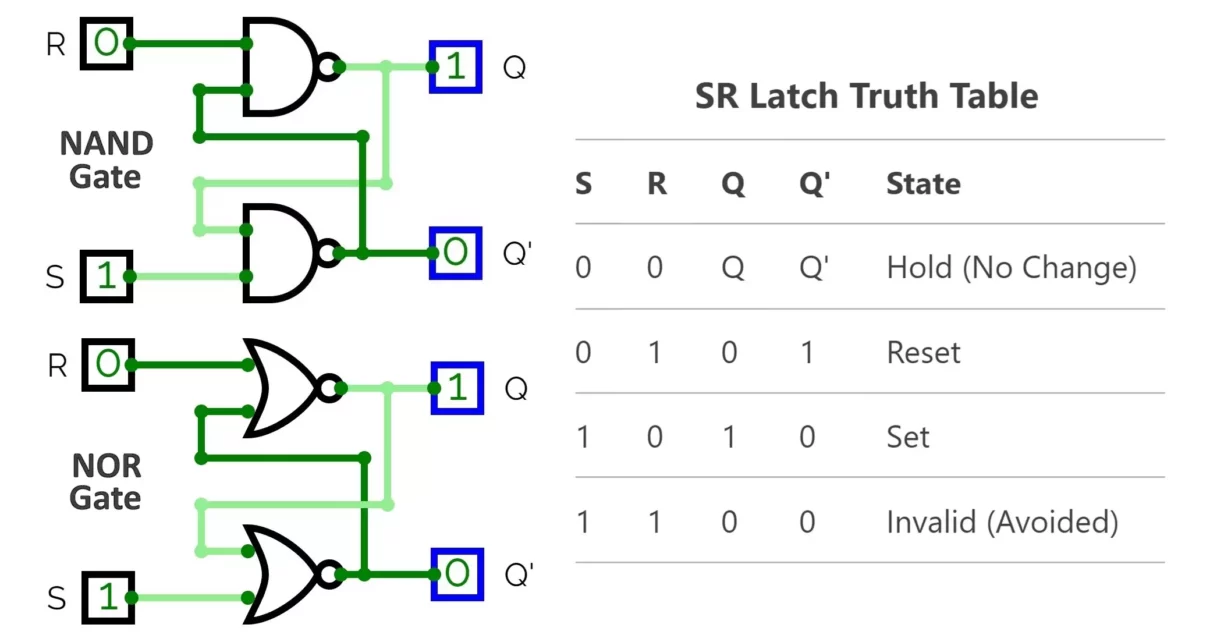

3. Truth Table of SR Latch

The truth table for an SR Latch depends on whether it is implemented using NOR gates or NAND gates. Below are the truth tables for both implementations:

NOR-Based SR Latch Truth Table

| S | R | Q | Q’ | State |

|---|---|---|---|---|

| 0 | 0 | Q | Q’ | Hold (No Change) |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | Set |

| 1 | 1 | 0 | 0 | Invalid (Avoided) |

NAND-Based SR Latch Truth Table

| S’ | R’ | Q | Q’ | State |

|---|---|---|---|---|

| 1 | 1 | Q | Q’ | Hold (No Change) |

| 1 | 0 | 0 | 1 | Reset |

| 0 | 1 | 1 | 0 | Set |

| 0 | 0 | 1 | 1 | Invalid (Avoided) |

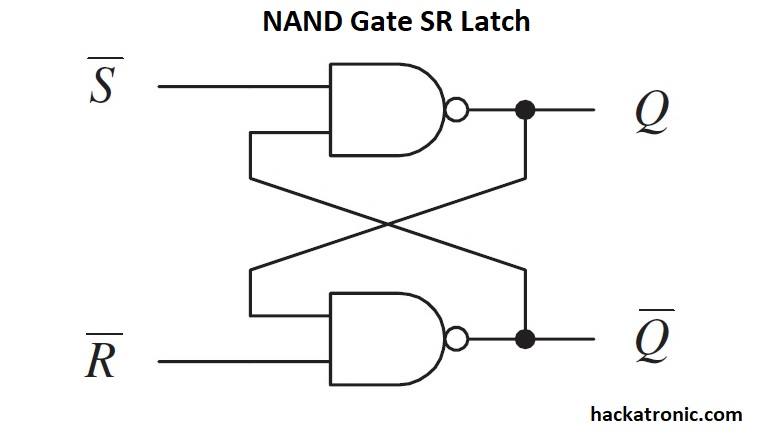

Note: In the NAND-based SR Latch, the inputs are active-low, meaning they are represented as S’ and R’.

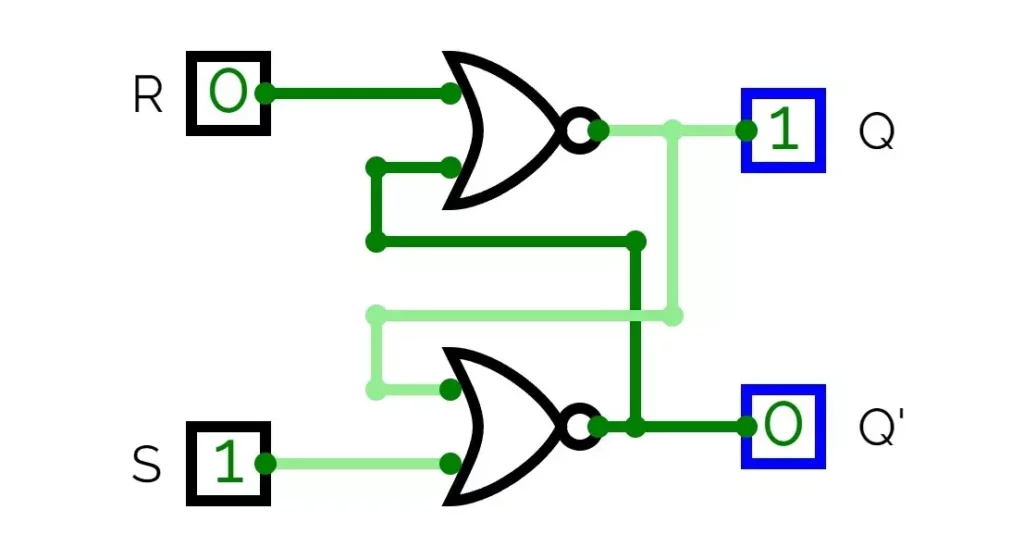

4. SR Latch Using NOR Gates

The SR Latch can be constructed using two NOR gates. The circuit diagram and working are as follows:

Circuit Diagram

Working

- When S = 1 and R = 0, the output Q becomes ‘1’, and Q’ becomes ‘0’ (Set state).

- When S = 0 and R = 1, the output Q becomes ‘0’, and Q’ becomes ‘1’ (Reset state).

- When S = 0 and R = 0, the latch holds its previous state.

- When S = 1 and R = 1, both Q and Q’ become ‘0’, which is an invalid state.

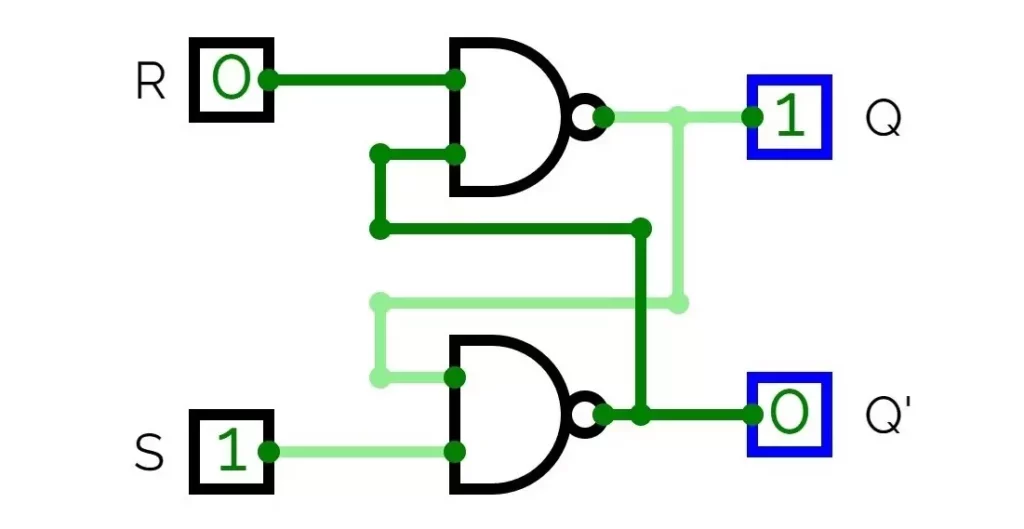

5. SR Latch Using NAND Gates

The SR Latch can also be constructed using two NAND gates. The circuit diagram and working are as follows:

Circuit Diagram

Working

- When S’ = 0 and R’ = 1, the output Q becomes ‘1’, and Q’ becomes ‘0’ (Set state).

- When S’ = 1 and R’ = 0, the output Q becomes ‘0’, and Q’ becomes ‘1’ (Reset state).

- When S’ = 1 and R’ = 1, the latch holds its previous state.

- When S’ = 0 and R’ = 0, both Q and Q’ become ‘1’, which is an invalid state.

6. SR Latch vs SR Flip-Flop

While both the SR Latch and SR Flip-Flop are used to store a single bit of information, there are key differences between them:

| Feature | SR Latch | SR Flip-Flop |

|---|---|---|

| Clock Signal | No clock signal (asynchronous). | Requires a clock signal (synchronous). |

| Operation | Responds immediately to input changes. | Responds only at clock edges (rising or falling). |

| Complexity | Simpler design. | More complex due to clock circuitry. |

| Applications | Used in basic memory circuits. | Used in sequential circuits like counters and registers. |

| Stability | Prone to glitches and race conditions. | More stable due to clock control. |

7. Advantages of SR Latch

- Simple Design – The SR latch has a basic circuit structure using NOR or NAND gates, making it easy to understand and implement.

- Memory Storage – It can store one bit of data, making it useful for memory applications.

- Asynchronous Operation – The latch does not require a clock signal, responding immediately to input changes.

- Fast Response – Since it’s level-triggered, it reacts quickly to input signals.

- Low Power Consumption – Requires minimal power compared to more complex flip-flops.

8. Disadvantages of SR Latch

- Invalid State (S=1, R=1 for NOR, S=0, R=0 for NAND) – This condition creates an indeterminate or unstable state.

- No Clock Control – Since it lacks a clock input, it continuously responds to changes, which can lead to unintended operations.

- Susceptible to Noise – Since it’s level-sensitive, small voltage fluctuations might trigger unwanted state changes.

- Limited Functionality – Cannot perform counting or toggling operations like other flip-flops (e.g., JK or D flip-flop).

- Not Suitable for Large-Scale Systems – Due to its simple design, more complex circuits need additional control mechanisms.

9. Applications of SR Latch

- Basic Memory Units – Used in small memory circuits for storing single-bit data.

- Debouncing Circuits – Helps stabilize signals from mechanical switches to prevent false triggering.

- Data Synchronization – Used in digital systems where level-triggered storage is required.

- Control Circuits – Used in devices like alarms, where ON/OFF states need to be maintained.

- Gating Logic – Used in logical control systems for enabling or disabling certain pathways.

- Sequential Logic Circuits – Acts as a building block for more complex flip-flops and registers.

10. Conclusion

The SR Latch is a simple yet powerful circuit that forms the foundation of many digital systems. Its ability to store a single bit of information makes it indispensable in memory and control applications. By understanding its working, truth table, and implementation using NAND and NOR gates, you can gain a deeper insight into digital logic design. Additionally, recognizing the differences between an SR Latch and an SR Flip-Flop helps in choosing the right component for specific applications.

IC 74LS279 and CD4044B are some of the very popular SR latch ICs. You can make SR latch by CD4001 IC, it is a quad 2 input NOR Gate IC. Whether you’re designing a basic memory circuit or a complex sequential system, the SR Latch remains a critical tool in your digital design toolkit.

What is Flip Flop Circuit? Types of Flip Flops with Truth Table

SR Flip Flop Truth Table, Circuit Diagram, Working and Applications